Unlocking High-Speed Logic Design: A Deep Dive into the Lattice GAL22V10D-7LJN CPLD

In the realm of digital logic design, where flexibility, integration, and speed are paramount, Complex Programmable Logic Devices (CPLDs) have long served as fundamental building blocks. Among these, the Lattice GAL22V10D-7LJN stands as a classic and highly influential workhorse, enabling designers to implement sophisticated combinatorial and sequential logic with remarkable efficiency. This article delves into the architecture and capabilities of this specific device, exploring why it remains a relevant tool for a wide array of applications.

At its core, the GAL22V10D is a 22V10 CPLD, a standard architecture pioneered by Lattice Semiconductor. The "22V10" nomenclature is telling: it offers up to 22 inputs and 10 output logic macrocells, providing a substantial amount of logic density for its category. Each macrocell is highly configurable, allowing designers to define its function as a registered (clocked) or combinatorial (unclocked) output. This programmability is achieved through a sum-of-products (SOP) logic array, where a programmable AND array feeds into a fixed OR array, granting the ability to create a vast number of logic functions.

The specific part number, GAL22V10D-7LJN, reveals its critical performance characteristics. The suffix `-7` denotes a maximum pin-to-pin propagation delay of 7.5 nanoseconds, classifying it as a high-speed variant. This swift response time is crucial for applications requiring rapid signal processing and deterministic timing, making it suitable for interfaces like high-speed state machines, address decoders, and bus control logic in microprocessor systems. The `LJN` portion identifies the package (PLCC-28) and the commercial temperature grade.

A key strength of the GAL22V10D architecture is its efficient and deterministic timing model. Unlike larger FPGAs where routing delays can be variable and complex to predict, the CPLD's predefined internal interconnect structure ensures that signal paths are consistent and fast. This predictability simplifies the design process, as engineers can confidently meet critical timing requirements without extensive post-layout analysis.

Furthermore, the device is based on electrically erasable (E²) CMOS technology, which allows for both easy reprogramming and zero-power standby modes. This reconfigurability is invaluable for prototyping and design iterations, while the low-power characteristics ensure energy efficiency in the final product.

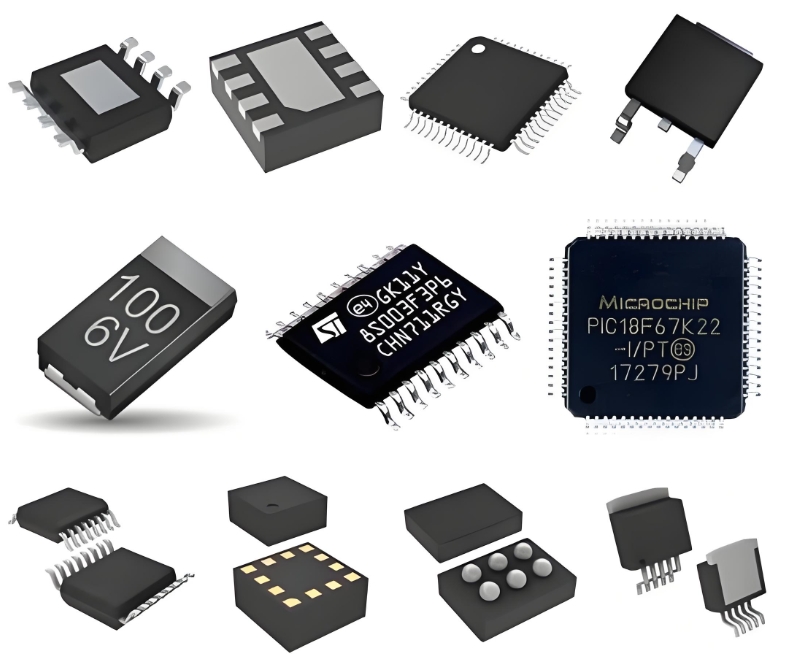

In practical terms, the GAL22V10D-7LJN excels in "glue logic" applications—the essential but often miscellaneous logic that ties together larger components on a board, such as CPUs, memory, and peripherals. It can consolidate dozens of discrete logic ICs (like the venerable 7400-series) into a single, compact chip, drastically reducing board space, component count, and overall system cost while improving reliability.

ICGOODFIND: The Lattice GAL22V10D-7LJN CPLD is a testament to enduring and effective digital design. It delivers a powerful blend of high-speed performance, design flexibility, and predictable behavior, making it an ideal solution for integrating control logic, implementing fast state machines, and reducing system complexity. For engineers seeking a reliable, proven, and straightforward programmable logic solution, this device continues to be an excellent choice.

Keywords: CPLD, High-Speed Logic, Programmable Logic Device, Sum-of-Products, Macrocell